इंटेल

इंटेल को 10nm नोड के लिए अपनी शिफ्ट के साथ महत्वपूर्ण समस्या थी और रिपोर्टों ने यह भी सुझाव दिया कि चिप कंपनी ने इसे पूरी तरह से डिब्बाबंद कर दिया था, लेकिन हमें आखिरकार इंटेल के आर्किटेक्चर इवेंट पर एक अद्यतन रोडमैप प्राप्त हुआ जिसने कुछ चिंताओं को कम करने में मदद की। संशोधित रोडमैप ने सनी कोव को प्रदर्शित किया जो 2019 में स्काइलेक को सफल करने वाला था और वास्तव में 10nm नोड पर था।

सनी कोव वास्तव में इंटेल के लिए बहुत महत्वपूर्ण है क्योंकि अभी तक कंपनी ने ताज़ा उत्पादों पर पुराने कोर का पुन: उपयोग किया है जो वास्तव में समुदाय के साथ अच्छी तरह से नीचे नहीं गए हैं। फिर AMD के Ryzen और उनके ज़ेन आर्किटेक्चर से लगातार खतरा बना हुआ है। एएमडी ने प्रतिस्पर्धात्मक उत्पादों पर प्रदर्शन अंतर को काफी हद तक बंद करने में कामयाबी हासिल की है और उन्होंने इंटेल के लाइनअप को बहुत खराब दिखाने के लिए अपने चिप्स की कीमत भी बहुत ही कम रखी है। यह इंटेल के सर्वर व्यवसाय को भी प्रभावित करता है क्योंकि एएमडी इस साल के अंत में ईपीवाईसी रोम सर्वर चिप्स जारी करेगा और प्रारंभिक लीक शानदार प्रदर्शन का सुझाव दें। सनी कोव आर्किटेक्चर पर निर्मित एक्सॉन चिप्स निश्चित रूप से इंटेल को सर्वर स्पेस में प्रतिस्पर्धा करने में मदद करेगा जहां वे काफी समय से एक प्रमुख बल रहे हैं।

सनी कोव - हाल के समय में इंटेल का सबसे बड़ा माइक्रोआर्किटेक्चर अपग्रेड

10nm में देरी के कारण Intel को प्रत्याशित की तुलना में 14nm लंबे समय तक रहना पड़ा। इसके परिणामस्वरूप बहुत से ताज़ा प्रक्षेपण हुए, जिसके परिणामस्वरूप केबी झील, कॉफी झील और व्हिस्की झील थी। यहां और वहां सुधार हुए लेकिन बहुत ज्यादा महत्वपूर्ण नहीं था। सनी कोव आखिरकार वह बदलने जा रहे हैं।

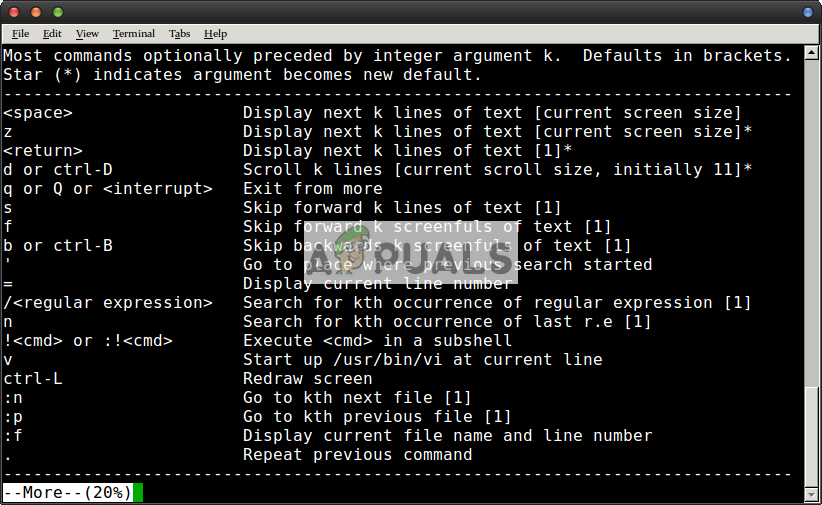

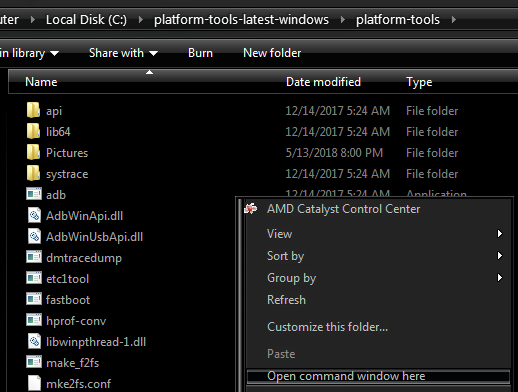

'वाइडर' फ्रंट एंड इम्प्रूवमेंट सोर्स - AnanadTech

'डीपर' फ्रंट एंड इम्प्रूवमेंट सोर्स - आनंदटेक

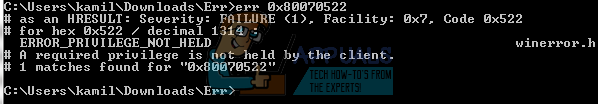

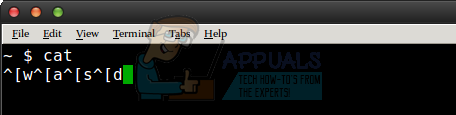

कच्चे आईपीसी आउटपुट में वृद्धि के अलावा सामान्य सुधार भी होंगे। उनके आर्किटेक्चर डे शोकेस में इंटेल ने 'वाइडर' और 'डीपर' के रूप में सुधारों का संदर्भ दिया। सनी कोव के पास बड़ा एल 1 और एल 2 कैश है, जिसमें 4. के बजाय 5-वाइड आवंटन भी हैं। निष्पादन बंदरगाहों में भी वृद्धि हुई है, सनी कोव में 8 से 10 तक जा रहा है।

आईपीसी में सुधार

इंटेल लेकफील्ड SoC

यह SoC सनी कोव कोर का उपयोग करने वाले पहले उत्पादों में से एक होगा और इसका उपयोग करने वाला पहला उत्पाद भी होगा Foveros 3D पैकेजिंग तकनीक । इंटेल ने हाल ही में अपने आगामी लेकफील्ड SoC के बारे में अधिक जानकारी दी है और वास्तव में बहुत उत्साहित है।

मूल रूप से यह एक हाइब्रिड सीपीयू है जो एक पैकेज में विभिन्न भागों में फिट होने के लिए स्टैकिंग का उपयोग करता है। पैकेज-ऑन-पैकेज स्टैकिंग वास्तव में मोबाइल SoCs के लिए बहुत आम है, लेकिन इंटेल थोड़ा अलग संस्करण का उपयोग करता है। सिलिकॉन पुलों के बजाय, फेवरोस तकनीक स्टैक के बीच एफ-टी-एफ माइक्रोबम्प्स का उपयोग करती है। Foveros पैकेजिंग भी घटकों को अलग-अलग मौतों में रखने की अनुमति देता है। इस तरह इंटेल उच्च प्रदर्शन कोर उर्फ सनी कोव कोर को और अधिक उन्नत 10nm प्रक्रिया पर रख सकता है, अन्य घटकों को चिप के 14nm प्रक्रिया भाग पर रखा जा सकता है। DRAM लेयर्स को ऊपर सीपीयू और GPU चिपलेट के साथ रखा जाता है और फिर बेस डाई को कैश और I / O के साथ रखा जाता है।

एक और दिलचस्प बात यहाँ का कार्यान्वयन है बड़े । X86 हार्डवेयर के साथ LITTLE । इसके मूल रूप से विभिन्न प्रकार के कार्यों के लिए दो प्रकार के प्रोसेसर का उपयोग किया जाता है, शक्तिशाली कोर का उपयोग संसाधन गहन कार्यों के लिए किया जाता है, इस प्रकार कम बिजली के कोर का उपयोग सामान्य कामकाज के लिए किया जाता है। लेकफ़ील्ड एक पाँच-कोर डिज़ाइन का उपयोग करता है, जिसमें चार निचले पावर कोर (एटम) और एक उच्च पावर कोर (सनी कोव) होता है। यह डिज़ाइन कार्यान्वित किया जाता है क्योंकि यह दक्षता में सुधार करता है क्योंकि विभिन्न कोर क्लस्टर्स के बीच प्रदर्शन को स्केल करना आसान होता है। लेकफ़ील्ड स्पष्ट रूप से मोबाइल उपकरणों, कॉम्पैक्ट लैपटॉप और अल्ट्राबुक की ओर लक्षित एक SoC है, लेकिन ज्यादातर इसकी क्वालकॉम के लिए इंटेल की प्रतिक्रिया है जो विंडोज उपकरणों के लिए अपने स्वयं के एआरएम SoCs को जारी करने के लिए कमर कस रहे हैं।

टैग इंटेल